等離子刻蝕中影響氮化硅側(cè)壁蝕刻傾斜度的參數(shù)有哪些?

文章導讀:在晶圓制造領(lǐng)域,使用等離子刻蝕不僅可以“吃掉”上層的光刻膠,也可以“吃掉”氮化硅薄膜, 形成一定的側(cè)壁蝕刻傾斜度。

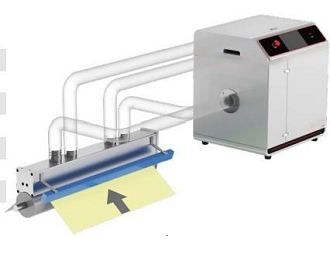

等離子表面處理系統(tǒng)能夠完成表面清洗、活化、刻蝕以及涂鍍等諸多功能,依據(jù)所需處理的材料與處理的目的,等離子表面處理系統(tǒng)能夠完成不同的處理效果。等離子表面處理設(shè)備在半導體方向的使用有等離子刻蝕、顯影、去膠、封裝等。

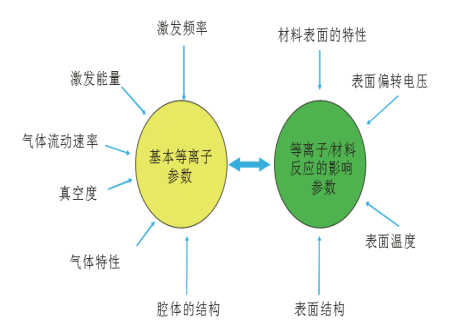

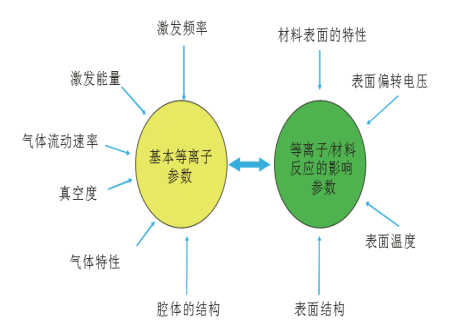

等離子刻蝕工藝在半導體集成電路中,既能夠刻蝕上表層的光刻膠,也能夠刻蝕基層的氮化硅層,不僅如此還需要防止其對硅襯底造成刻蝕損害,從而造成器件暗電流增大,影響產(chǎn)品良率,為達到這諸多條件的工藝要求。等離子刻蝕工藝能夠通過對真空等離子表面處理設(shè)備的部分參數(shù)調(diào)整,形成一些氮化硅層的特殊形貌,即側(cè)壁蝕刻傾斜度。

等離子刻蝕工藝在半導體集成電路中,既能夠刻蝕上表層的光刻膠,也能夠刻蝕基層的氮化硅層,不僅如此還需要防止其對硅襯底造成刻蝕損害,從而造成器件暗電流增大,影響產(chǎn)品良率,為達到這諸多條件的工藝要求。等離子刻蝕工藝能夠通過對真空等離子表面處理設(shè)備的部分參數(shù)調(diào)整,形成一些氮化硅層的特殊形貌,即側(cè)壁蝕刻傾斜度。

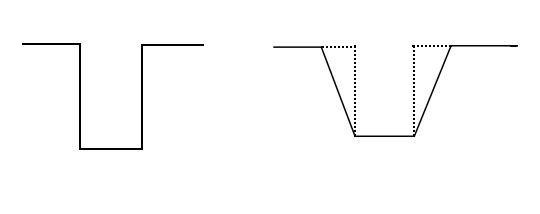

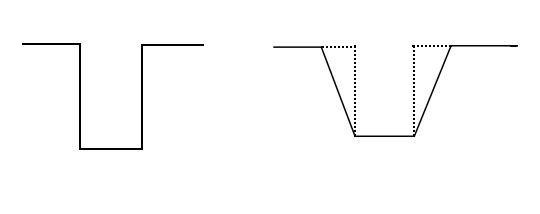

側(cè)壁蝕刻傾斜度的優(yōu)勢在于,當具有一定程度的傾斜度時,可以有效降低金屬鍍膜層在階梯覆蓋時出現(xiàn)斷裂的幾率,以及改善集成電路中工藝金屬線路內(nèi)部斷裂的問題。如下所示是氮化硅側(cè)壁垂直和具有一定程度的傾斜度的示意圖:

通過多次的變量測試和實驗,我們可以通過真空度、等離子發(fā)生器的功率、CF4流量、O2流量、氣體流量比、腔內(nèi)壓強以及處理時間等不同變量的研究,能夠找到一個適合的氮化硅層側(cè)壁刻蝕傾角。

普樂斯電子9年專注研制等離子清洗機,等離子表面處理設(shè)備,已通過ISO9001質(zhì)量體系和歐盟CE認證,為電子、半導體、汽車、yi療等領(lǐng)域的客戶提供清洗,活化,刻蝕,涂覆的等離子表面處理解決方案。如果您想要了解更多關(guān)于產(chǎn)品的詳細內(nèi)容或在設(shè)備使用中有疑問,歡迎點擊普樂斯的在線客服進行咨詢,或者直接撥打全國統(tǒng)一服務(wù)熱線400-816-9009,普樂斯恭候您的來電!

蘇公網(wǎng)安備 32058302002178號

蘇公網(wǎng)安備 32058302002178號